# FDSOI 28nm performances study for RF energy scavenging

Edouard Rochefeuille, Frédéric Alicalapa, Alexandre Douyère, Tan-Phu Vuong

### ▶ To cite this version:

Edouard Rochefeuille, Frédéric Alicalapa, Alexandre Douyère, Tan-Phu Vuong. FDSOI 28nm performances study for RF energy scavenging. IEEE Radio and Antenna Days of the Indian Ocean (IEEE RADIO 2017), Sep 2017, Cape Town, South Africa. pp.012009, 10.1088/1757-899X/321/1/012009. hal-01742478

## HAL Id: hal-01742478 https://hal.univ-reunion.fr/hal-01742478v1

Submitted on 22 Aug 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

#### **PAPER • OPEN ACCESS**

# FDSOI 28nm performances study for RF energy scavenging

To cite this article: E Rochefeuille et al 2018 IOP Conf. Ser.: Mater. Sci. Eng. 321 012009

View the article online for updates and enhancements.

#### **Related content**

- <u>Cmos spdt switch for wlan applications</u> M A S Bhuiyan, M B I Reaz, L F Rahman et al.

- <u>Simulation and performance study of</u> <u>ceramic THGEM</u> Yan Jia-Qing, Xie Yu-Guang, Hu Tao et al.

- <u>Study of atmospheric muon interactions in</u> <u>Si nanoscale devices</u> P. Li Cavoli, G. Hubert and J. Busto

# IOP ebooks<sup>™</sup>

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

#### IOP Conf. Series: Materials Science and Engineering **321** (2018) 012009 doi:10.1088/1757-899X/321/1/012009

### FDSOI 28nm performances study for RF energy scavenging

#### E Rochefeuille<sup>1,2</sup>, F Alicalapa<sup>1</sup>, A Douyère<sup>1</sup> and T P Vuong<sup>2</sup>

<sup>1</sup>LE2P, EA 4079, Faculté des Sciences et Technologies, Université de la Réunion, 97744 Saint-Denis Cedex 9, Réunion

<sup>2</sup>IMEP-LAHC, UMR 5130, Institut Polytechnique de Grenoble, 38016 Grenoble Cedex, France

E-mail : edouard.rochefeuille@phelma.grenoble-inp.fr

Abstract. This paper presents a study on an integrated technology: Fully-Depleted-Silicon-On-Insulator (FDSOI) at a 28nm node. FDSOI results are compared to another technology: Complementary-Metal-Oxide-Semiconductor (CMOS) 350nm. The aim of this work was to demonstrate the advantages of using FDSOI technology in RF energy scavenging applications. Characteristics of transistors are pointed out and results showed an improved 22%-output voltage gain for a series rectifier and a 13%-output voltage gain for a Dickson charge pump in FDSOI technology compared to CMOS, for an input voltage and power of 0.5 V and 0 dBm respectively. Those results allowed to prove that FDSOI 28nm is a better technology choice for energy scavenging and low-power applications.

#### 1. Introduction

Nowadays, microelectronic field aims to focus more and more on systems miniaturization as the reduction of power consumption without compromises on the required performances. Based on these objectives, some studies have been realized on energy conversion applications in [1], [2] and [3]. In addition to that, energy scavenging applications are considered to reduce the power consumption as in [4]. Moreover, reducing size could make evolve circuits like shown in [5]. RF energy scavenging is also present at nanoelectronic scale, which is designed to power integrated low-energy devices and sensors. The primary features and challenges of the FDSOI compared to CMOS has been described in literature as in [6]. Based on these facts, the aim of this study was to compare two technologies and to point out the advantage to use the emergent technology FDSOI in integrated applications such as RF-DC and DC-DC (charge pump) conversions applied to energy scavenging and low-power. This paper offers comparison simulations between CMOS 350nm and FDSOI 28nm technologies. Section 2 describes the remarkable transistors parameters. Then, the obtained output voltages of an RF rectifier and a Dickson charge pump structure [7] are discussed in section 3 and 4. Simulations were realized with Cadence Software by considering raw components. The ultimate goal of this study was to demonstrate that FDSOI 28nm is a suitable technology for RF energy scavenging.

#### 2. Transistors characteristics

#### 2.1. Transistors threshold voltages

This subsection presents studies of the drain current curves of different transistors of the technologies. FDSOI 28nm offers two interesting N-channel transistors: LVT (Low Voltage Threshold) and RVT (Regular Voltage Threshold). For CMOS technology, this work focuses on the

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI. Published under licence by IOP Publishing Ltd 1 N-channel NMOS only. The following simulation gave the voltage threshold of the transistors by plotting the drain current Id for a drain voltage (Vds) of 1V and a gate voltage (Vgs) that varies from - 1 V to +3 V. Results showed a voltage threshold of 200 mV for the LVT and 400 mV for the RVT in FDSOI 28nm. The same simulation was done for the NMOS transistor in CMOS 350nm. A threshold of 600 mV was found for the NMOS. These results show the best possible performances in FDSOI for low-power applications. Table 1 shows the threshold values.

|                                                     | FDSOI  | FDSOI  | CMOS   |  |  |  |

|-----------------------------------------------------|--------|--------|--------|--|--|--|

|                                                     | LVT    | RVT    | NMOS   |  |  |  |

| Threshold Voltage                                   | 200 mV | 400 mV | 600 mV |  |  |  |

| Table 1 Threshold values of the studied transistors |        |        |        |  |  |  |

**Table 1.** Threshold values of the studied transistors

#### 2.2. Diode-connected transistor substrate connexion

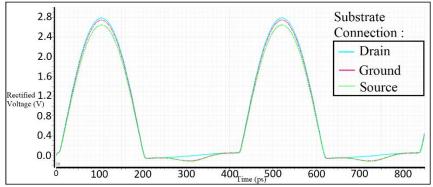

This subsection presents a better way to connect the substrate connection of a fourconnections transistor in diode-connected mode. The four-possible connexions are Gate, Drain, Source and Substrate. According to schematic on figure 2 and results on figure 1, the rectifying process performed better when substrate was connected to gate and drain. The advantages were therefore a good rectification with less current in negative part and a higher voltage. Figure 1 shows limits of the substrate connexion.

Figure 1. Transistors substrate connexion effect on rectified voltage

#### 3. Rectifier

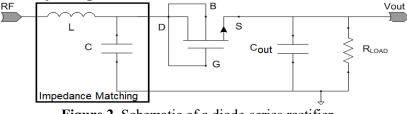

This section presents a comparison between simulated results obtained with a simple RF-DC rectifier, where the diode was replaced by LVT, RVT or NMOS transistors in diode-connected mode. Figure 2 shows the corresponding schematic.

Figure 2. Schematic of a diode-series rectifier

The input power was set to 0 dBm at a frequency of 2.4 GHz. The output capacitance was set to 160 pF and the load resistance to 1 G $\Omega$  in order to show the best output voltages in this case. Figure 3a shows the output responses of the rectifier without using the impedance matching.

IOP Conf. Series: Materials Science and Engineering 321 (2018) 012009 doi:10.1088/1757-899X/321/1/012009

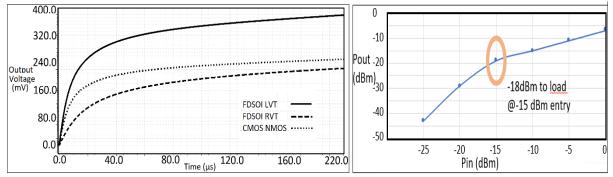

Figure 3a. Output voltages of rectifier

Figure 3b. Output power of an impedance matched rectifier

As shown on figure 3a, the use of a FDSOI LVT transistor allowed a simple rectifier to produce 390 mV output while the output voltage reaches only 240 mV in CMOS technology. The performance gain was therefore 22% on an RF simulated output voltage in favour of FDSOI technology. These performances came from the fact that FDSOI LVT threshold is lower than CMOS and this last parameter is linked to the rectifying diode-mode connection. The RVT transistor is not better than the NMOS in this case because it's default channel length is 4 times bigger than LVT. Channel length is a critical parameter in energy scavenging, more than channel width. Figure 3b shows the output power of a matched L-C rectifier for an input power that goes from -25 dBm to 0 dBm. The matching network allowed a maximum power transfer between the input generator and the transistor. A decent efficiency of 52% at -15 dBm was reached.

#### 4. Charge Pump

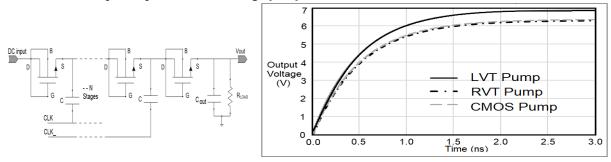

This section presents a comparison between simulated results obtained with a classic 4stages Dickson charge pump shown in [7] where the diode-connected transistors are replaced by LVT, RVT or NMOS. The input voltage was set to 0.5 V, the clock Vpp was 1V with a frequency of 100 KHz and the output resistance was 100 M $\Omega$ . Figure 4a shows the charge pump schematic and figure 4b shows the output responses of the charge pump.

Figure 4a. Charge pump schematic

Figure 4b. Output voltages of charge pump using different transistors

As shown in figure 4b, the charge pump that operates with LVT diode-connected transistors achieved better performances than RVT and NMOS responses. The output voltage was 7 V for LVT charge pump while it was higher than 6 V for RVT and CMOS. In this case, a nearly 13%-output voltage improvement was scored by LVT response compared to CMOS because of its low voltage. In addition, it is important to mention that default dimensions of LVT are smaller than NMOS, typically a hundred nano-meters compared to a dozen of micro-meters.

To go further, a 4-stages Dickson circuit was simulated using optimal parametric values with FDSOI LVT. The pump performed up to 3V-output voltage from a 250mV-input with no load. An optimized circuit gave an output of 600 mV at 160  $\mu$ A. Table 2 compares this work to literature.

IOP Conf. Series: Materials Science and Engineering **321** (2018) 012009 doi:10.1088/1757-899X/321/1/012009

| Work             | [1] Moisiadis<br>2000 | [2] Bhalerao<br>2007 | [3] Chen<br>2010      | This work       |        |

|------------------|-----------------------|----------------------|-----------------------|-----------------|--------|

| Type of work     | Simulation            | Simulation           | 1-Chip<br>Integration | Simulation      |        |

| Process          | Standard CMOS         | Standard CMOS        | 65nm CMOS             | 28nm FDSOI      |        |

| Number of stages | 4                     | 4                    | 3                     | 4-Dickson based |        |

| Input-Voltage    | 1.2 V                 | 1.5 V                | 0.18 V                | 0.25            | 1.5 V  |

| Output Voltage   | 3.5 V                 | 6 V                  | 0.5 V                 | 0.6             | 11.4 V |

| Gain             | 2.9                   | 4                    | 2.78                  | 2.4             | 9.5    |

| Load             | ~58 kΩ                | ~133 kΩ              | 50 kΩ                 | 3750 Ω          | 133 kΩ |

| Output-Power     | $\sim 210 \ \mu W$    | ~270 µW              | 5 µW                  | 96 μW           | 969 μW |

#### Conclusion

Table 2. Work comparison

This paper presents a study on two integrated technologies for RF energy scavenging. FDSOI 28nm and CMOS 350nm performances was compared. The FDSOI LVT transistor was particularly pointed out for its best voltage threshold and characteristics that allow higher output voltages over CMOS in low-voltage RF-DC and DC-DC conversions while reducing the overall dimensions. FDSOI technology is more expensive than CMOS but offers many advantages as a smaller die size and better performances. These comparison results lead to the choice of FDSOI technology for the design of a complete integrated rectifying module for RF energy scavenging.

#### Acknowledgement

The Autor would like to thank the Reunion Island Regional Council and the European Union – European Regional Development Fund (FEDER) PO 2014-2020 for their financial support to this work.

#### References

- [1] Y Moisiadis, I Bouras and A Arapoyanni, "A CMOS charge pump for low voltage operation," 2000 IEEE International Symposium on Circuits and Systems. Geneva, vol.5, pp. 577-580, 2000.

- [2] S A Bhalerao, A V Chaudhary and R M Patrikar, "A CMOS Low Voltage Charge Pump," *20th International Conference on VLSI Design*, Bangalore, pp. 941-946, 2007.

- [3] Po-Hung Chen *et al.*, "0.18-V input charge pump with forward body biasing in startup circuit using 65nm CMOS," *IEEE Custom Integrated Circuits Conference 2010*, San Jose, CA, pp. 1-4, 2010.

- [4] T Paing, E A Falkenstein, R Zane and Z Popovic, "Custom IC for Ultralow Power RF Energy Scavenging," in *IEEE Transactions on Power Electronics*, vol. 26, no. 6, pp. 1620-1626, June 2011.

- [5] A Douyère, S Rivière, J Rivière, F Alicalapa, J-D Lan Sun Luk, "Conception et réalisation d'un convertisseur RF/DC dédié à la collecte de faibles niveaux de puissance," *Journées Nationales Microondes*, May 2013, Paris, France, 2013, HAL<01137832>.

- [6] D H Triyoso *et al.*, "Extending HKMG scaling on CMOS with FDSOI: advantages and integration challenges," *2016 International Conference on IC Design and Technology (ICICDT)*, Ho Chi Minh, pp. 1-4 2016.

- J F Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," in *IEEE Journal of Solid-State Circuits*, vol. 11, no. 3, pp. 374-378, Jun 1976.