# Co-simulation of a complete rectenna with a circular slot loop antenna in CPW technology

Jérôme Rivière, Alexandre Douyère, Jonathan Cazour, Frédéric Alicalapa, Jean-Daniel Lan Sun Luk

# ▶ To cite this version:

Jérôme Rivière, Alexandre Douyère, Jonathan Cazour, Frédéric Alicalapa, Jean-Daniel Lan Sun Luk. Co-simulation of a complete rectenna with a circular slot loop antenna in CPW technology. Radio and Antenna Days of the Indian Ocean, Sep 2017, Cape Town, South Africa. 10.1088/1757-899X/198/1/012005. hal-01631299

# HAL Id: hal-01631299 https://hal.univ-reunion.fr/hal-01631299

Submitted on 10 Nov 2017

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **PAPER • OPEN ACCESS**

# Co-simulation of a complete rectenna with a circular slot loop antenna in CPW technology

To cite this article: Jérôme Rivière et al 2017 IOP Conf. Ser.: Mater. Sci. Eng. 198 012005

View the article online for updates and enhancements.

### Related content

- DC-pass filter design with notch filters superposition for CPW rectenna at low power level

- J Rivière, A Douyère, F Alicalapa et al.

- Experimental study of rectenna coupling at low power level

A Douyère, F Alicalapa, S Rivière et al.

- Fabrication and Characterization of n-AlGaAs/GaAs Schottky Diode for Rectenna Device Application

Norfarariyanti Parimon, Farahiyah Mustafa, Abdul Manaf Hashim et al.

# Co-simulation of a complete rectenna with a circular slot loop antenna in CPW technology

Jérôme Rivière, Alexandre Douyère, Jonathan Cazour, Frédéric Alicalapa and Jean-Daniel Lan Sun Luk

University of La Reunion, Laboratory of Electronic, Energetic and Process St Denis, Reunion Island

jerome.riviere@univ-reunion.fr

**Abstract**. This study starts with the design of a planar and compact CPW antenna fabricated on Arlon AD1000 substrate,  $\varepsilon_r$ =10.35. The antenna is a coplanar waveguide (CPW) fed circular slot loop antenna matched to the standard impedance 50  $\Omega$  by two stubs. The goal is to implement this antenna with a CPW RF/DC rectifier to build an optimized low power level rectenna. The rectenna design is restricted to allow easy and fast fabrication of an array with a high reproducibility. The full rectenna is simulated and achieves 10% effciency at -20 dBm.

#### 1. Introduction

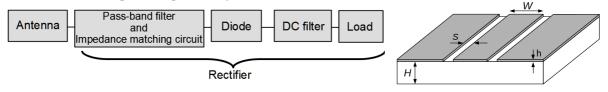

Lastly, with the growth of wireless communications and the development of smart cities, energy harvesting has received considerable attention [1]. Wireless communication developments tend to provide reliable and constant wireless energy. Those electromagnetic waves convey information but they are also energy carriers. The majority of the communicative devices spread their signals to all directions in space and so energy is wasted in the environment. The rectenna depict in figure 1 converts electromagnetic waves to DC voltage and can harvest this energy to power small devices. Robustness and repeatability in rectenna should be as perfect as possible to limit differences across samples of the same model. Moreover, many applications need power characteristics that require the use of an array of antenna. But, as the complexity of antenna and frequency number increase, phase shifting and complex matching impedance circuitry are needed. Another solution relies on rectenna arrays, which combine several rectenna DC voltages to power a device. This second solution requires reliable and accurate rectenna conception.

This work is dedicated to rectenna arrays solution. In order to suppress vias in rectenna conception we use CPW (Figure 2) [2]. In this technology, the conductive line width W and the ground plane are etched on the same plane, separated by a slot of width S on each side of the conductive line.

**Figure 1.** Synoptic figure of a rectenna

Figure 2. CPW structure

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

The topic of this paper focuses on the design and conception of a planar and compact antenna to be used with a RF/DC rectifier in CPW technology. This antenna is also simple and fast to realize on a CNC machine as few processing steps are required. It consists of a patch surrounded by a ground conductor on the same plane of the substrate, without background metallization to avoid the connection of a transition to the ungrounded CPW rectifier.

This paper begins with the conception and measurement of the CPW-fed circular slot antenna. In this section we have developed the steps leading to the final antenna design. The next section summarizes the conception of the CPW rectifier. Finally, the antenna is simulated with the rectifier and the efficiency is evaluated using an accurate diode model optimized for 2.45 GHz.

## 2. Antenna Design and measurement

#### 2.1. Design

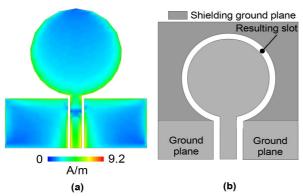

The antenna for this rectenna conception is a modified CPW fed circular slot loop antenna (or coplanar patch antenna). The study starts with a circular monopole antenna because it is one of the simplest patterns to study [3]. Only two parameters were optimized: patch radius ( $\mathbf{R}$ ) and distance ( $\mathbf{d}$ ) between patch and the ground. To facilitate fabrication process of the rectenna, we set the slot widths in all our designs to the 0.787 mm milling tool we use to etch the rectenna. The simulated initial antenna (Figure 3.a) shows a large bandwidth of 2.7 GHz, with a gain G of 1.4 dBi and directivity of 3.16 dBi. The return loss is of -28 dB at 2.45 GHz, and the total dimensions of the patch are 45\*60 mm<sup>2</sup>.

When plotting the current distribution of the patch at 2.45 GHz (Figure 3,a), we can notice that the current propagates along the edge of the circular patch and is "null" at the top of the circular monopole pattern. Hence, shielding the patch with a ground plane compels the magnetic field to propagate along the newly created slot (Figure 3.b); thus increasing the current at the edges while maintaining similar resonant frequency.

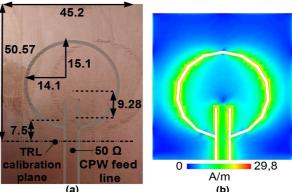

Shielding the circular pattern has indeed increase the current propagating along the edge of the antenna. This modification also modifies the frequency of operation and impedance. To correct the frequency shift, a diminution of the patch radius is sufficient. To match the 50  $\Omega$  impedance required from the rectifier we use stubs impedance matching technique because it offers advantages in the antenna design, such as size reduction. Hence, two stubs are inserted inside the radiating element to match the antenna impedance at 50  $\Omega$  (Figure 4.a). This solution gives a more compact antenna with a shorter feed line. Plus, the width of the feeding line remains equal to the width W of the rectifier conductive line.

It can be noted that the radius of the final circular patch is closed to the radius of the monopole antenna with only 0,5 mm difference. The use of stub in this case, because of the nature of the CPW feeding line can also be seen as a movement of the feed-point closer to the center of the circular patch. Thus, the antenna size is reduced to 45.2\*50.57 mm<sup>2</sup> with a gain of 2.34 dBi, directivity of 3.87 dBi and peak current of 29.8 A/m (Figure 4.b).

Figure 3. (a) Initial antenna current propagation and Figure 4. (a) CPW-fed circular slot loop antenna with antenna

(b) Monopole antenna transformation to slot loop dimensions in mm and (b) current propagation of the proposed antenna

#### 2.2. Measurement

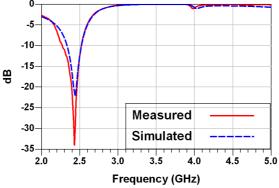

The proposed antenna is realized and measured (Figure 5). Measurement presents a bandwidth  $\boldsymbol{B}$  of 250 MHz and return loss of -23.7 dB at 2.45 GHz. The simulation and measurement show good agreement with a small frequency drift  $\Delta \boldsymbol{F}$  of 10 MHz. To measure this antenna, we use TRL calibration technique. This allows us to take into account part of the ground plane, which will be added by the rectifier on the antenna performances [4].

Figure 5. Reflection coefficient of the simulated and realized antenna

#### 3. Rectenna simulation

#### 3.1. Rectenna conception summary

In order to evaluate the complete rectenna efficiency, we use a co-simulation under Schematics environment on Advanced Design System 2013. Each element of the rectenna has been optimized to ease and speed up realization time, but has also been modified to reduce the rectenna dimensions. Those aspects of this work should be further addressed in a different paper when dealing with the global rectenna conception. For the purpose of this paper we will only focus on the co-simulated rectenna efficiency.

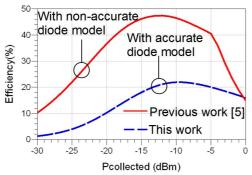

In our previous work [5], the HSMS7630 diode model used was composed of a generic diode component filled with SPICE model from the data sheet. We then upgraded this model to take into account the effect of the diode surrounding such as CPW line, soldering and parasitic effects of the diode body. But this model turned out to be ineffective, because it did not properly modeled the DC behaviour of the diode.

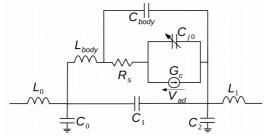

To fix this issue, we use a different model (Figure 6) in which we first model the DC behaviour of the diode with a current generator  $G_c$  driven by the voltage  $V_{ad}$ . Afterward, modifications were made to model the diode frequency behaviour through the fitting of the model generated S parameters and measured ones. The effectiveness of this model has been primarily verified with the comparison between simulated and measured impedance of a sub-part of the rectenna made with the CPW DC filter in [7] and the diode.

Figure 6. Diode model

This comparison is done at the particular diode polarization voltage of 84 mV. This voltage in simulation gives the best efficiency with a load of 5.7 k $\Omega$  and a lossless impedance matching between the generator and the circuit. A difference in phase has been noticed, which could be explained by the

block-to-block co-simulation. This process, hence does not take into account the coupling effect in practice between the elements.

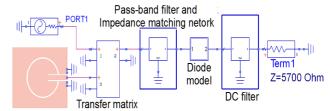

#### 3.2. Simulation

The simulated results of the rectenna are compared to our previous results [5] (Figure 7). In both simulations, we use S-parameters of the simulated CPW elements of the DC filter and the input-matching network. We simulate the full rectenna at 2.45 GHz and choose a L-matching impedance network realized in CPW technology. This matching technique is simple, uses fewer components and avoids the use of component mounted in surface. In this work, we use the antenna impedance in the simulation. To do so, a S-parameter block is used which allows the rectifier to only see the antenna impedance while being powered by the generator (Figure 8).

**Figure 8.** Schematics view of the simulated rectenna at 2.45 GHz

Figure 7. Simulated rectenna efficiency

#### 4. Conclusion

In this work a compact CPW-fed circular slot loop antenna is designed and measured. We show that such an antenna can be derived from a circular monopole antenna as a starting point. Those modifications reduce the bandwidth and the size of the antenna, but improve the gain at the desired frequency. This design is interesting because it has several advantages over the well-known patch antenna; such as, bad impedance matching at first higher order harmonics, larger bandwidth than a microstrip patch antenna, bi-directional radiation pattern in the opposite direction of space and antenna size reduction.

The simulation of a complete rectenna in CPW technology is performed with a more accurate diode model than our previous work [5]. The rectifier is composed of a single series diode HSMS7630. The diode is modeled through I/V characteristics and S-parameter fitting between diode model and measurement at low power level. The simulation of the rectenna shows rectifying efficiency of 10% at 2.45 GHz for  $P_{in}$ =-20 dBm and a resistive load  $R_{load}$ =5,7 k $\Omega$ .

### Acknowledgment

This work received financial support from Reunion island Regional Council and Union European – European Regional Develoment Fund (FEDER)

### References

- [1] C. Perera, A. Zaslavsky, P. Christen and D. Georgakopoulos 2014 Context aware computing for the internet of things: A survey IEEE communications survey & tutorials vol. 16

- [2] R. Simons 2001 Coplanar Waveguide Circuits, Components, and Systems ed John Wiley

- [3] L. Xian 2012 Ultra-Wideband Antenna and design

- [4] N. Zhu and R. W. Ziolkowski *2012* Metamaterial-inspired GPS L1 rectennas Antenna Technology (iWAT) IEEE International Workshop on p. 193–196.

- [5] J.Rivière, A. Douyère, F. Alicalapa and J.-D Lan Sun Luk 2016 DC-pass filter design with notch filters supperposition for CPW rectenna at low power level IOP Conf. Ser. Mater. Sci. Eng. vol.120